Home

Thanks to the miniaturization increasing quickly, it is possible to design ever more efficient architectures. However the components in these architectures are ever more complex to design. Indeed, the components have to comply with ever more strict constraints, in terms of costs, size and consumption, while keeping a certain level of performance.

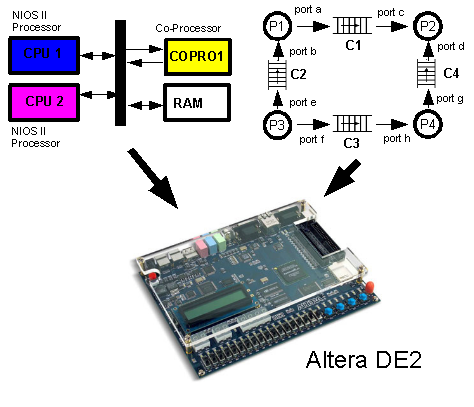

In order to get such architectures, one solution is to combine instruction set processors allowing some flexibility, with dedicated components less flexible but more efficient.

With Altera DE2 cards, the design software suite, and the components library, it is possible to implement such architectures. TaskMapper uses these tools, and simplifies a tedious task by making transparent implementation of communications between the differents resources.

So TaskMapper offers a graphical MPSoC edition tool (Kahn Process Network, architecture model, placement model), and a code generator tool to implement this MPSoC on the Altera DE2 card.