## FERMAT | Sandeep Shukla | June 2005 shukla@vt.edu

## ESL: Panacea or Hype?

Acknowledgement: NSF, Project Espresso @IRISA, FERMAT @Virginia Tech, and the "Chip Design" Magazine

#### **Outline**

- Pictures speak louder than words

- What is ESL?

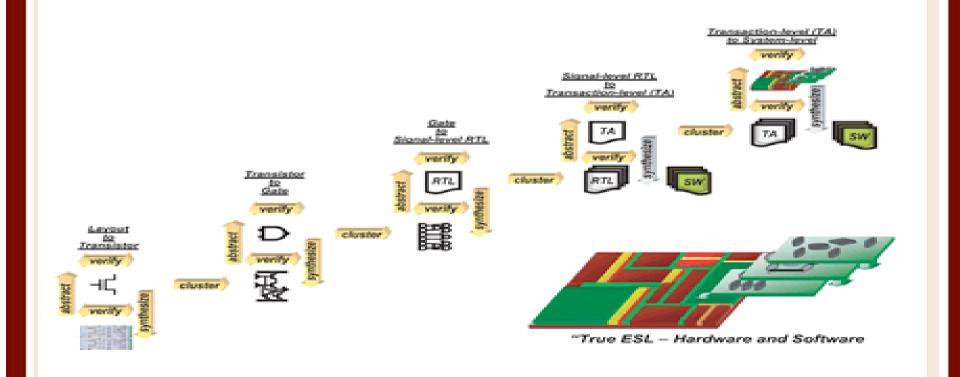

- Abstraction Trends

- Verification Trends

- \_ EDA Industry Trends

- What are we doing?

- \_ Heterogeneity and MoCs

- Behavioral Hierarchy

- \_ Meta Modeling Support

- Service Oriented Validation Framework

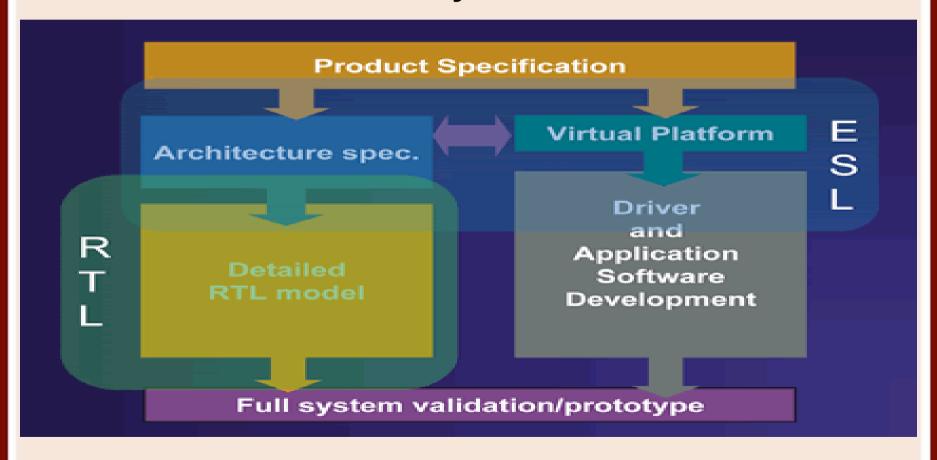

#### Electronic System Level?

#### **Abstraction Trends**

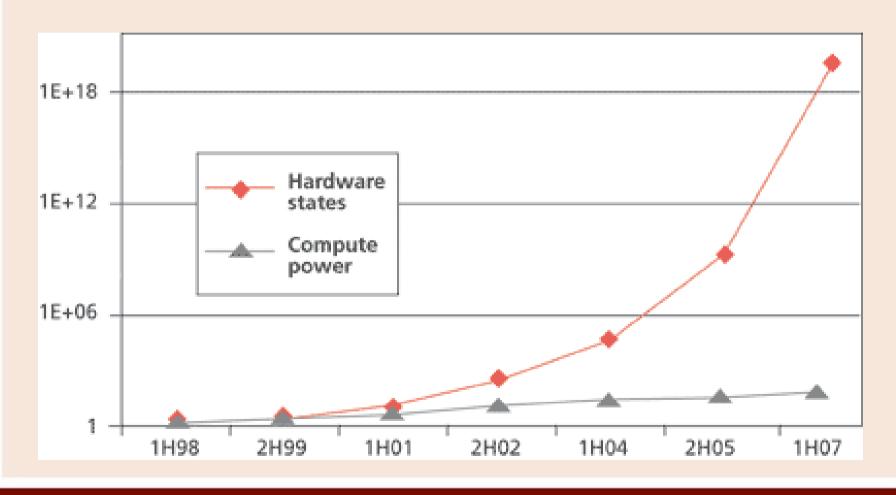

## Hardware Resources and Computer Power

#### A Tale of Two ESLs?

|                                                         | SystemC                                             | SystemVerilog                                                                                           |

|---------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Core abstration level                                   | Events and messages                                 | Logic states and transitions                                                                            |

| Architectural design                                    | System-level hardware view and SW programmer's view | HW implementation view;<br>DPI link to C/C++/SystemC                                                    |

| Architectural verification<br>and HW/SW co-verification | Cycle accurate<br>TLM@ >10,000 cps                  | Timing accurate RTL @<br>1-10 cps; TLM capability;<br>C-like extensions for<br>algorithmic descriptions |

| RTL-to-gates design                                     | No gate-level modeling                              | Logic synthesis                                                                                         |

| RTL-to-gates verification                               | TLM/RTL co-stimulation                              | Implementation testbench,<br>including ABV and<br>functional coverage                                   |

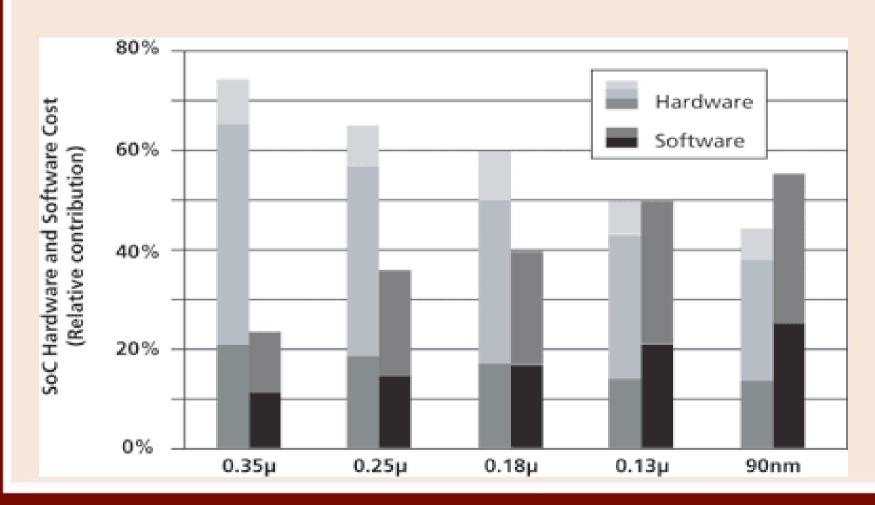

#### HW/SW Cost Breakdown Trends

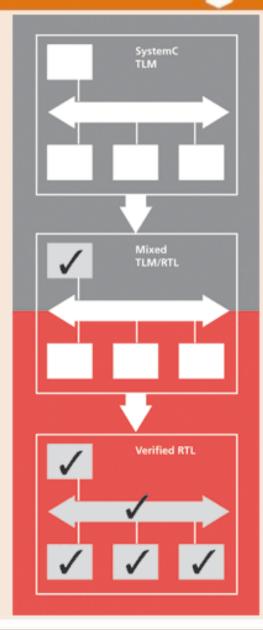

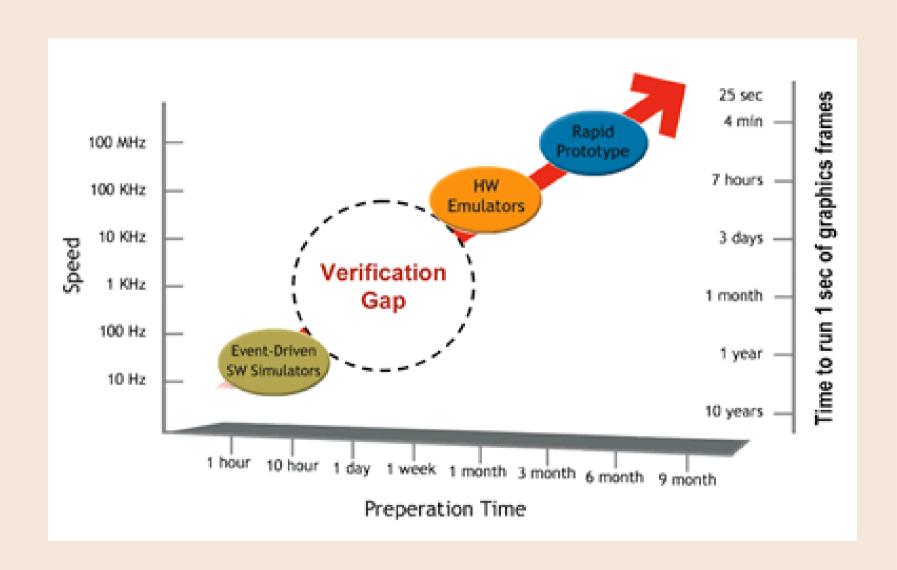

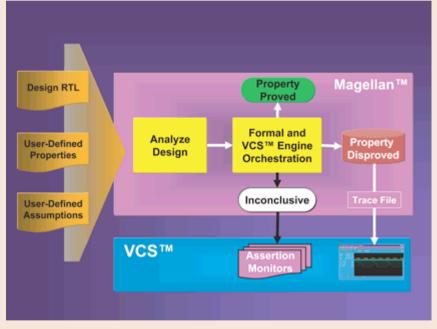

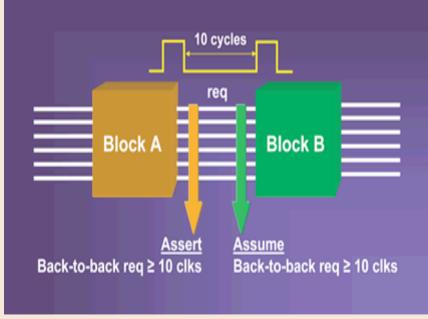

#### **Verification Trends**

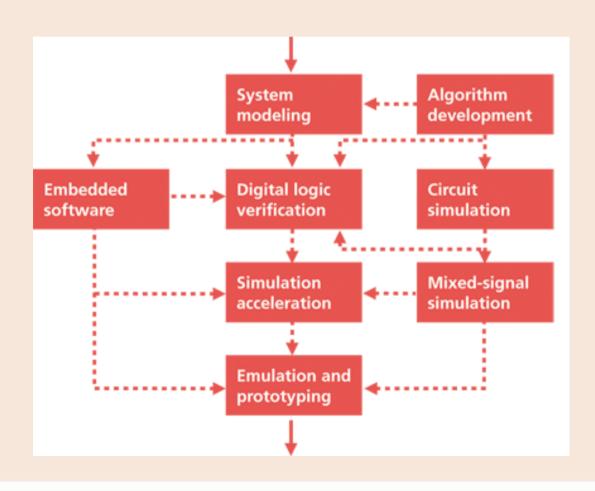

### Hybrid and AMS

#### **Verification Trends**

## **ESL Industry Space**

| Company                                            | Location                         | Design Style                 | Design<br>Language                   | Capatilities                                                                                                                                                               | Uri                         |

|----------------------------------------------------|----------------------------------|------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| ACE Associated<br>Compiler<br>Experts by           | Amsterdam,<br>The<br>Netherlands | Embedded                     | C/C++                                | Compiler generators & testing tools for compilers                                                                                                                          | www.ace.nl                  |

| Aldec, Inc.                                        | Henderson,<br>NV                 | SoC                          | C/C++,<br>Handel-C,<br>Verilog, VHDL | ASIC 8 high-density FPGA<br>verification environment                                                                                                                       | www.aldec.com               |

| Alternative<br>System<br>Concepts, Inc.            | Windham,<br>NH                   | Embedded                     | XML, Verilog,<br>VHDL                | Sehavioral synthesis software<br>tool to reduce power<br>consumption                                                                                                       | www.ascinc.com              |

| Altera Corp.                                       | San Jose,<br>CA                  | Embedded                     | C, MATLAB,<br>proprietary            | Automates adding,<br>parameteriting, & linking<br>embedded processors,<br>co-processors, peripherals,<br>memories, user-defined logic for<br>system-on-a-programmable-chip | www.altera.com              |

| Ansoft Corp.                                       | Pittsburgh,<br>PA                | Component                    | VHDL-AMS                             | Mixed-technology designs<br>prevalent in automotive industry                                                                                                               | www.ansoft.com              |

| ARM Ltd<br>(acquired AKYS<br>Design<br>Automation) | Cambridge,<br>ux                 | SoC                          | C/C++,<br>SystemC, LISA              | Simulation, debugging, analysis,<br>verification. Cycle and<br>functionally accurate virtual<br>prototyping. Transaction-based<br>abstraction level                        | www.arm.com                 |

| DiveSpec                                           | Waltham,<br>MA                   | Behavioral                   | SystemVenlog                         | SystemVenlog-based behavioral synthesis                                                                                                                                    | www.bluespec.com            |

| Cadence Design<br>Systems, Inc.                    | San Jose,<br>CA                  | Behavioral<br>Co-Ventication | C/C++,<br>SystemC,<br>Venlog, VHDL   | Transaction-level model development & verification, algorithm development, hardware-softmare verification                                                                  | www.cadence.com             |

| Carbon Design<br>Systems                           | Waltham,<br>MA                   | Behavioral                   | C. Verilog.<br>VHDL                  | Virtual hardware models from<br>Verilog and/or VHDL                                                                                                                        | www.carbondesignsystems.com |

| CARDtools<br>Systems                               | Sen Jose,<br>CA                  | SoC, embedded                | C/C++                                | Modeling hardware, software, b<br>systems at different levels of<br>abstraction                                                                                            | www.cardtools.com           |

| Catalytic Inc.                                     | Palo Alto.                       | SoC, embedded                | MATLAB from                          | Signal processing algorithm                                                                                                                                                | www.catalyticine.com        |

#### Our Work at FERMAT and ESPRESSO

- Introduce Heterogeneity in SystemC with Models of Computation (MoC) extensions

- Raise the Modeling Fidelity

- Step towards Behavioral Hierarchy with Heterogeneity

- EWD: Meta-Modeling Frameworks

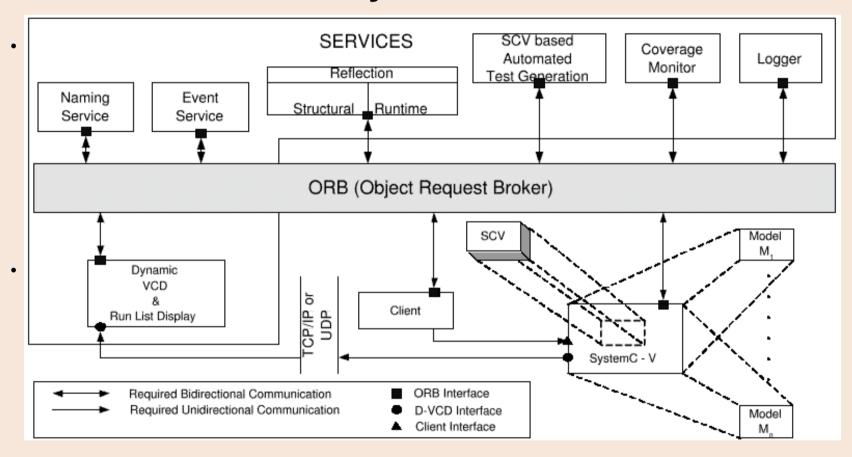

- CARH: Service Oriented Validation Framework

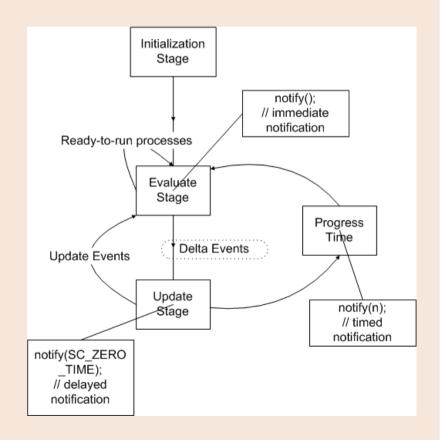

#### SystemC's Discrete-Event Kernel

- Evaluate-Update Paradigm

- Dynamic scheduling incurs unnecessary delta cycles

- Statically schedulable MoCs should avoid dynamic scheduling

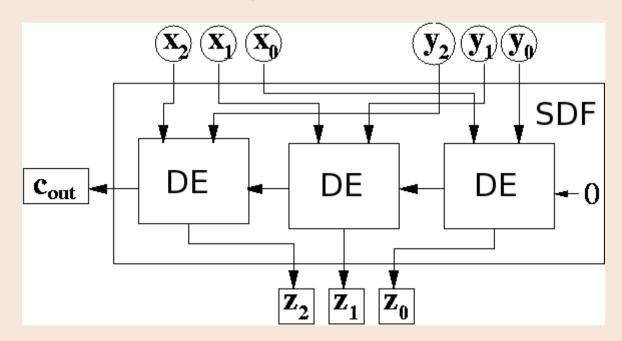

## An Example MoC Extension: Synchronous Data Flow in SystemC

- SDF models are:

- Amenable to static scheduling

- Require blocks to have predefined production and consumption rates

- Construct repetition vector

- Construct firing order

- Executable schedule achieved with valid repetition vector and firing order

## An Example MoC Extension: Synchronous Data Flow in SystemC

```

SC_MODULE( toplevel )

sc_in_clk CLK;

SC_THREAD( topentry ) {

sensitive << CLK.pos();</pre>

SC_CTOR ( toplevel ) {

// Instantiate SDF blocks and connect

// the ports

void topentry() {

sdf_trigger();

```

## An Example MoC Extension: Synchronous Data Flow in SystemC

- During initialization all executable schedules are computed

- DE kernel continues executes without intervention until sdf\_trigger() is invoked

- SDF kernel takes over and executes the SDF-specific blocks according to the computed schedule

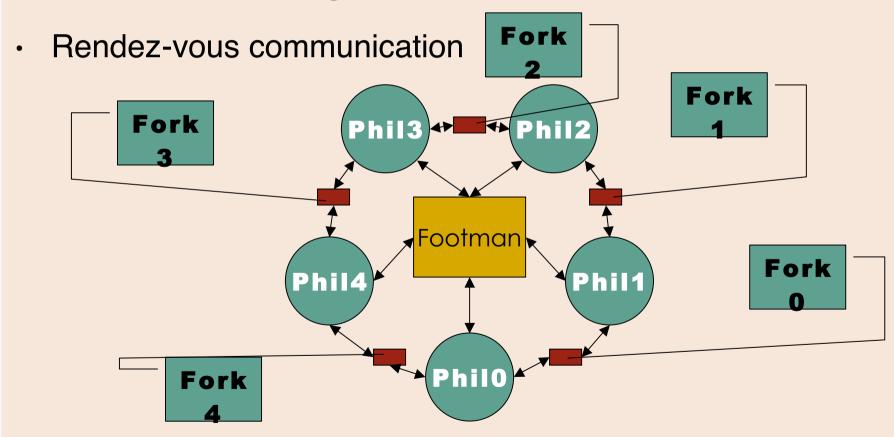

## Heterogeneous Extensions Communicating Sequential Processes

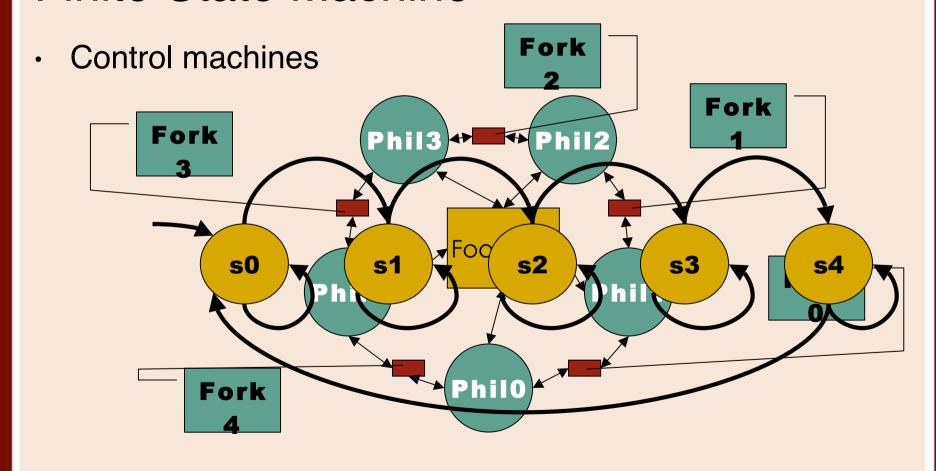

### Heterogeneous Extensions Finite State Machine

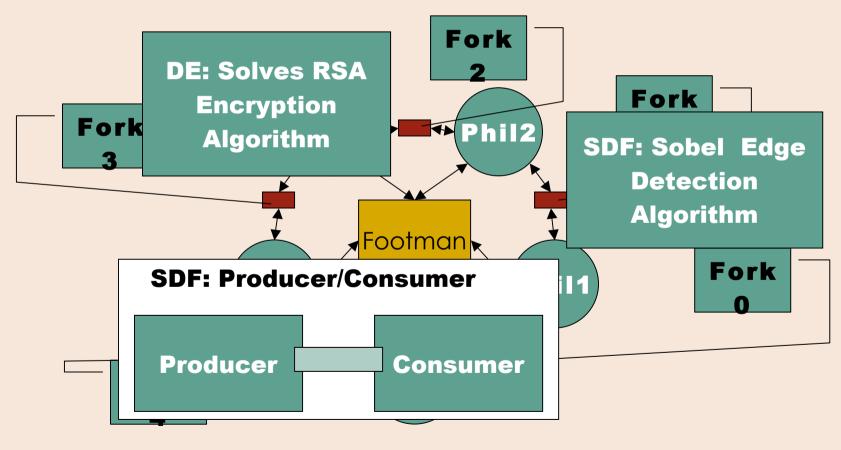

# Heterogeneous Extensions DE, FSM, SDF & CSP

### Simulation Efficiency A brief look

- Pure SDF models ~ 65% gains

- Pure FSM models ~ 10% degradation

- Pure CSP models ~ 1% gains

## Behavioral Hierarchy with Heterogeneity

- Decompose design into small behaviors

- Behaviors expressed by different MoCs

### Behavioral Hierarchy with Heterogeneity

- Semantics define interactions within MoC and across MoCs

- Hierarchical composition preserves behavioral hierarchy

#### Why you want GreenSocs

SystemCXML: <a href="http://systemcxml.sourceforge.net">http://systemcxml.sourceforge.net</a>

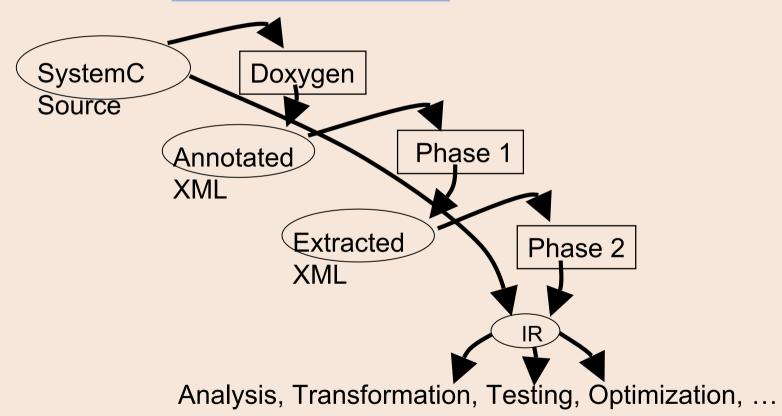

#### What we do with SystemC?

#### Reference

Website for SystemC-H: <a href="http://fermat.ece.vt.edu/systemc-h/">http://fermat.ece.vt.edu/systemc-h/</a>

Book